Interfaces « XJTAG DFT Assistant » pour CAO électronique

Sur un marché de l’électronique soumis à une forte concurrence, l’efficacité et la rapidité du test des produits ont un impact significatif sur le délai de mise sur le marché et par voie de conséquence sur le bilan du global projet. Par ailleurs la densité des circuits imprimés ne cessant d’augmenter, il devient de plus en plus difficile de prévoir des accès aux broches situées sous de nombreux boitiers pour les tests en cours de fabrication, notamment pour les boitiers BGA.

La technologie Boundary Scan (JTAG) a été conçue pour offrir un accès de test, et une conception JTAG optimisée permet d’avoir un effet positif sur le retour sur investissement.

Avec les outils XJTAG, découvrez comment faire de l’approche DFT (Design For Test) un aspect essentiel de votre processus de conception.

La technologie Boundary Scan (JTAG) a été conçue pour offrir un accès de test, et une conception JTAG optimisée permet d’avoir un effet positif sur le retour sur investissement.

Avec les outils XJTAG, découvrez comment faire de l’approche DFT (Design For Test) un aspect essentiel de votre processus de conception.

Interfaces DFT gratuites pour identifier les problèmes en amont :

La conception en vue du test (DFT) permet d’éviter de coûteuses reprises de circuits. Pour ces raisons, XJTAG a conçu des extensions « XJTAG® DFT Assistant » disponibles pour les principaux outils CAO du marché :

La conception en vue du test (DFT) permet d’éviter de coûteuses reprises de circuits. Pour ces raisons, XJTAG a conçu des extensions « XJTAG® DFT Assistant » disponibles pour les principaux outils CAO du marché :

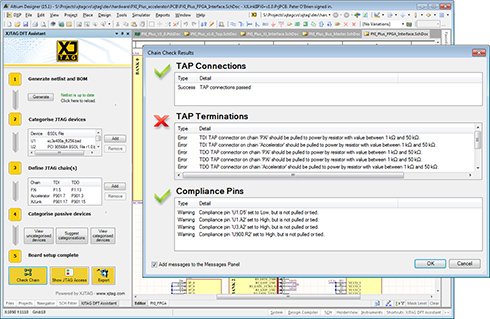

Ces interfaces sont des logiciels gratuits de « Conception en vue du test » (Design for test) développés par XJTAG, parfaitement intégrables dans les environnements CAO cités ci-dessus.

Ces assistants permettent aux ingénieurs de détecter et de corriger les erreurs JTAG sur les cartes électroniques dés le stade de la conception, c’est-à-dire bien avant l’entrée en production. Du fait de leur type de boitier, de nombreux circuits intégrés sont inaccessibles aux sondes de test par contact physique, aussi ne pas fournir l’accès JTAG à ces puces pourrait entraîner des reprises coûteuses de la carte, ainsi que du retard sur les projets en cours.

L’Assistant DFT identifie les problèmes de testabilité potentiels pendant l’étape de saisie de schéma, en validant la mise en œuvre correcte des chaînes « Boundary Scan », ainsi que la conformité aux pratiques exemplaires de conception en vue du test.

De plus, la conformité à la norme JTAG peut également fournir d’autres avantages, notamment le débogage de prototypes et la programmation de périphériques plus rapides, ainsi que des tests de fabrication plus rapides et plus rentables

Ces assistants permettent aux ingénieurs de détecter et de corriger les erreurs JTAG sur les cartes électroniques dés le stade de la conception, c’est-à-dire bien avant l’entrée en production. Du fait de leur type de boitier, de nombreux circuits intégrés sont inaccessibles aux sondes de test par contact physique, aussi ne pas fournir l’accès JTAG à ces puces pourrait entraîner des reprises coûteuses de la carte, ainsi que du retard sur les projets en cours.

L’Assistant DFT identifie les problèmes de testabilité potentiels pendant l’étape de saisie de schéma, en validant la mise en œuvre correcte des chaînes « Boundary Scan », ainsi que la conformité aux pratiques exemplaires de conception en vue du test.

De plus, la conformité à la norme JTAG peut également fournir d’autres avantages, notamment le débogage de prototypes et la programmation de périphériques plus rapides, ainsi que des tests de fabrication plus rapides et plus rentables

Principales fonctions :

L’Assistant DFT comprend deux éléments clés : le « XJTAG Chain Checker » et le « XJTAG Access Viewer » :

L’Assistant DFT comprend deux éléments clés : le « XJTAG Chain Checker » et le « XJTAG Access Viewer » :

Après une configuration simple et rapide, XJTAG Chain Checker analyse la netlist et trouve une chaîne d’analyse JTAG routable. Il identifie les erreurs de connexion et en informe le développeur au cours du processus de conception. Les erreurs de terminaison incorrecte des ports TAP sont également identifiées.

XJTAG Access Viewer « superpose » le périmètre de test « bounday scan » sur le schéma, ce qui permet à l’utilisateur de savoir instantanément quels composants sont accessibles à l’aide de l’outil « boundary scan » et où la couverture de tests peut être étendue. Les ingénieurs peuvent mettre en évidence les interconnexions séparément, en vue d’afficher sur le schéma les accès en lecture, écriture, les alimentations, ainsi que les interconnexions sans accès JTAG.

Bénéfices :

Développés par XJTAG, ces plugins gratuits « Assistant DFT » pour les logiciels de schématique électronique augmentent de façon significative les capacités de « conception en vue du test » et du débogage de l’environnement de schématique et de conception de circuits imprimés.

La solution JTAG ayant été conçue pour faciliter le test de circuits imprimés (PCB) très denses et incluant notamment des boîtiers tels que les types BGA, il est donc d’une importance vitale que la chaîne JTAG fonctionne parfaitement dès le stade de la saisie de schéma.

Le fait de ne pas identifier et de ne pas corriger les erreurs de conception en amont peut entraîner une reprise du PCB, ainsi qu’un retard coûteux du projet en cours.

Pendant que le premier prototype est en cours de fabrication, l’assistant XJTAG DFT permet aux ingénieurs d’exporter un projet XJTAG préliminaire à partir de l’environnement CAO vers l’environnement de développement de test complet XJDeveloper où d’autres tests supplémentaires peuvent être réalisés. La carte peut ensuite être testée dès sa disponibilité.

Pour plus d’informations sur le sujet, vous pouvez consultez le document « Recommandations pour la conception en Vue du Test (DFT) », qui constitue un guide de référence couvrant de nombreux cas rencontrés.

Développés par XJTAG, ces plugins gratuits « Assistant DFT » pour les logiciels de schématique électronique augmentent de façon significative les capacités de « conception en vue du test » et du débogage de l’environnement de schématique et de conception de circuits imprimés.

La solution JTAG ayant été conçue pour faciliter le test de circuits imprimés (PCB) très denses et incluant notamment des boîtiers tels que les types BGA, il est donc d’une importance vitale que la chaîne JTAG fonctionne parfaitement dès le stade de la saisie de schéma.

Le fait de ne pas identifier et de ne pas corriger les erreurs de conception en amont peut entraîner une reprise du PCB, ainsi qu’un retard coûteux du projet en cours.

Pendant que le premier prototype est en cours de fabrication, l’assistant XJTAG DFT permet aux ingénieurs d’exporter un projet XJTAG préliminaire à partir de l’environnement CAO vers l’environnement de développement de test complet XJDeveloper où d’autres tests supplémentaires peuvent être réalisés. La carte peut ensuite être testée dès sa disponibilité.

Pour plus d’informations sur le sujet, vous pouvez consultez le document « Recommandations pour la conception en Vue du Test (DFT) », qui constitue un guide de référence couvrant de nombreux cas rencontrés.